Two revolutionary design methods result in substantial enhancements in efficiency in fractional-N part locked loops (PLLs), report scientists from Tokyo Tech.

The proposed strategies purpose to attenuate undesirable alerts often called fractional spurs, which usually plague PLLs utilized in many fashionable radar techniques and wi-fi transceivers. These efforts may open doorways to technological enhancements in wi-fi communication, autonomous autos, surveillance, and monitoring techniques in past 5G period.

Many rising and evolving applied sciences, resembling self-driving autos, goal monitoring techniques, and distant sensors, depend on the high-speed and error-free operation of wi-fi information transceivers and radar techniques. In these functions, part locked loops (PLLs) are essential elements that assist with the synthesis, modulation, and synchronization of oscillating alerts. Thus, eliminating or minimizing sources of error in PLLs is crucial to enhance the general efficiency of techniques.

In fractional-N PLLs, a well-liked kind of PLL with wonderful decision and versatile management of frequency, jitter and fractional spurs are mainstay enemies. “Jitter” refers back to the general deviation from the perfect timing of the synthesized oscillation. Then again, fractional spurs are undesirable alerts that come up from the periodicity within the error.

Parts known as digital-to-time converters (DTCs) are usually used within the digital PLLs to cancel the quantization error, however imperfections in DTCs resulting from so-called “integral non-linearities (INLs)” in the end manifest as fractional spurs that degrade part noise within the output of the PLL.

A analysis workforce from Tokyo Institute of Know-how (Tokyo Tech), led by Professor Kenichi Okada, sought to deal with these issues by way of the event of two revolutionary design methods resulting in a low-spur fractional-N PLL. Their work has been printed within the Continuing of the 2024 IEEE Worldwide Strong-State Circuits Convention (ISSCC).

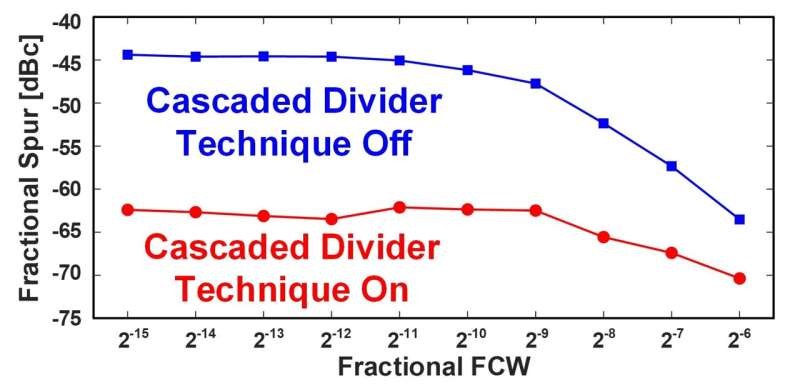

The primary proposed approach entails using a cascaded-fractional divider. This methodology entails splitting the frequency management phrase (FCW), an inner PLL sign that controls the output frequency, into two however in a approach that each are removed from an integer worth.

The logic underlying that is that for far-integer FCWs, fractional spurs seem within the PLL in increased frequencies, and high-frequency elements are naturally filtered out by the inherent operations of the PLL. Notably, this strategy doesn’t contain digital pre-distortion (DPD), a method that introduces complexity and causes slower part locking.

The second proposed approach revolves round a pseudo-differential DTC to keep away from the pitfalls of ordinary DTC implementations.

“In typical DTC designs, there are stringent trade-offs between the DTC energy, delay vary, noise, and INL, limiting the minimal fractional-spur stage achievable,” explains Prof. Okada. To sort out this challenge, the researchers famous that the non-linearities of DTCs include even symmetric elements. Accordingly, they carried out the perform of a single DTC utilizing two half-range DTCs with the identical even-symmetric INLs in differential operation. Consequently, these INLs had been naturally canceled out by way of subtraction on the PLL’s part detector.

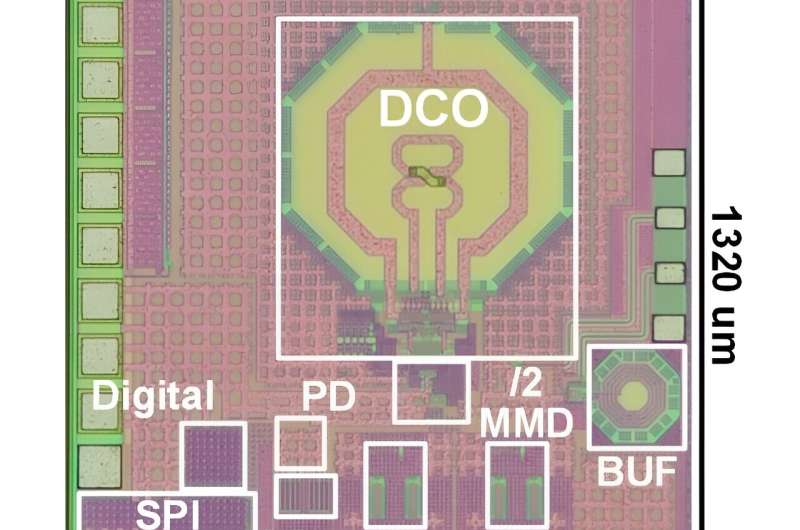

The workforce examined their concepts by implementing the proposed digital PLL utilizing a 65 nm CMOS course of, requiring an lively circuit space of solely 0.23 mm2. By evaluating the efficiency of their system with different state-of-the-art designs, the researchers famous a number of benefits.

“By suppressing fractional spurs, the built-in PLL jitter was diminished from 243.5 fs to 143.7 fs,” says Prof. Okada. “Due to the proposed cascaded fractional divider and pseudo-differential DTC methods, we achieved the bottom class of jitter with out DPD know-how.”

This revolutionary design might result in technological enhancements throughout many functions the place fractional-N PLLs are a mainstay.

Extra info:

A 7GHz Digital PLL with Cascaded Fractional Divider and Pseudo-Differential DTC Attaining -62.1dBc Fractional Spur and 143.7fs Built-in Jitter, Continuing of the 2024 IEEE Worldwide Strong-State Circuits Convention (ISSCC)

Tokyo Institute of Know-how

Quotation:

Combating fractional spurs in part locked loops to enhance wi-fi system efficiency in past 5G (2024, February 16)

retrieved 17 February 2024

from https://techxplore.com/information/2024-02-combating-fractional-spurs-phase-loops.html

This doc is topic to copyright. Other than any truthful dealing for the aim of personal examine or analysis, no

half could also be reproduced with out the written permission. The content material is supplied for info functions solely.